数字IC设计-格雷码

格雷码是一种循环二进制编码,特点是相邻数变化时只有一位数据跳变。

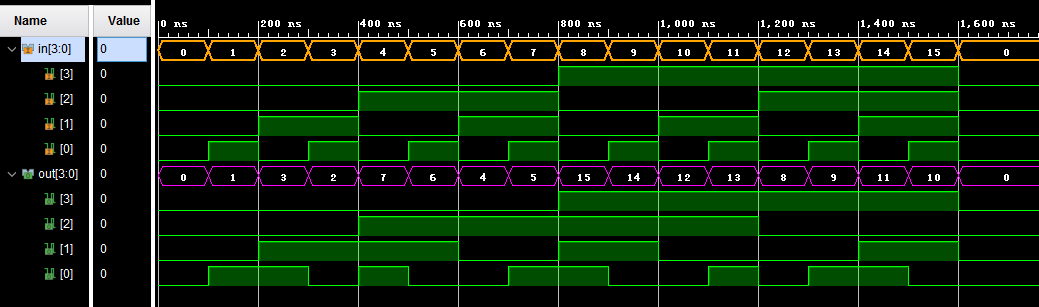

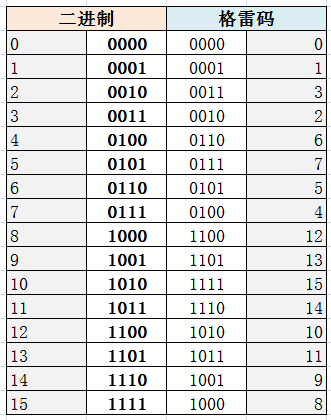

- 4位二进制和格雷码对应如下:

1、二进制到格雷码转换

- Verilog实现

1 | module bin_to_gray |

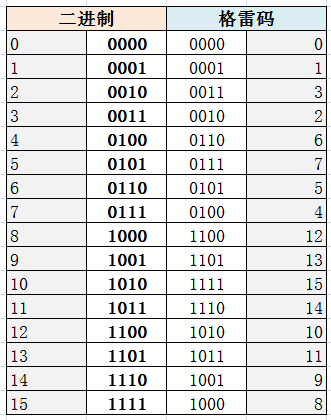

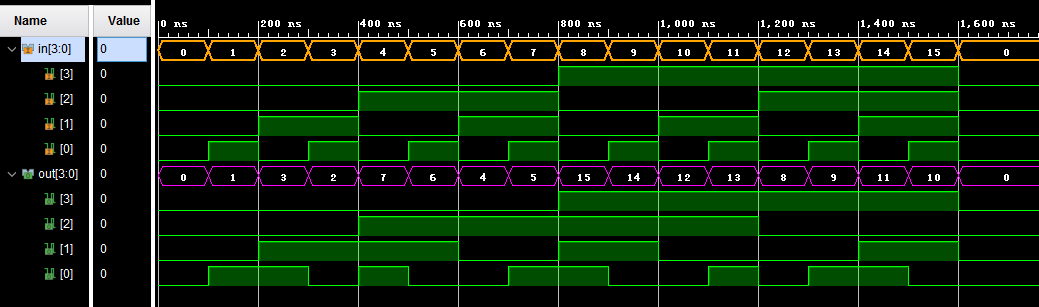

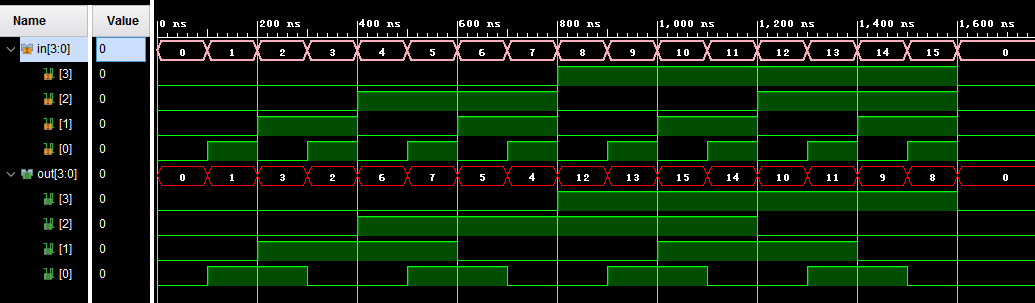

- 仿真波形:

2、格雷码转二进制

- Verilog实现:

1 | module gray_to_bin |

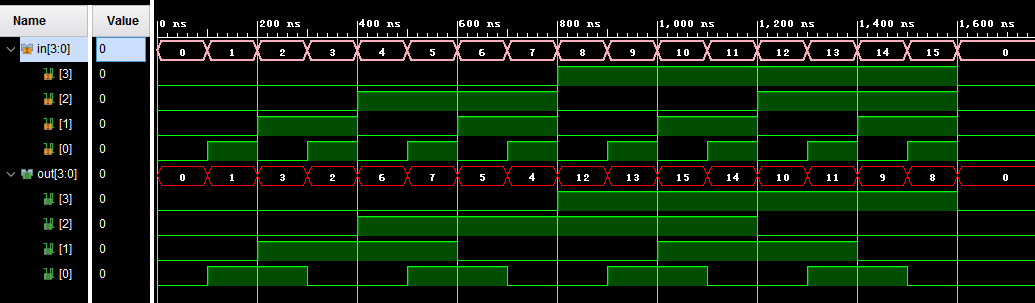

- 仿真波形:

著作权归本网站(https://makerinchina.cn)所有,转载请注明来自 MakerInChina.

格雷码是一种循环二进制编码,特点是相邻数变化时只有一位数据跳变。

1 | module bin_to_gray |

1 | module gray_to_bin |