Quartus-Altera FPGA开发-建立简单的LED工程

使用Quartus开发FPGA,这里建立一个简单的LED工程;

1 新建项目

1.1 项目设置

打开Quartus,点击File -> New Project Wizard,然后根据向导选择项目的路径,项目名字,顶层模块名称;

1.2 器件选择

在device设置页面,选择硬件型号,这里使用的 Cyclone系列,型号 EP13CT144C8;

1.3 工具选项

在EDA Tools设置中选择 simulation为ModelSim;

2 编写Verilog模块

2.1 新建Verilog代码

点击 New -> Verilog HDL File,新建一个文件,再写一点东西进行保存;

2.2 编写模块

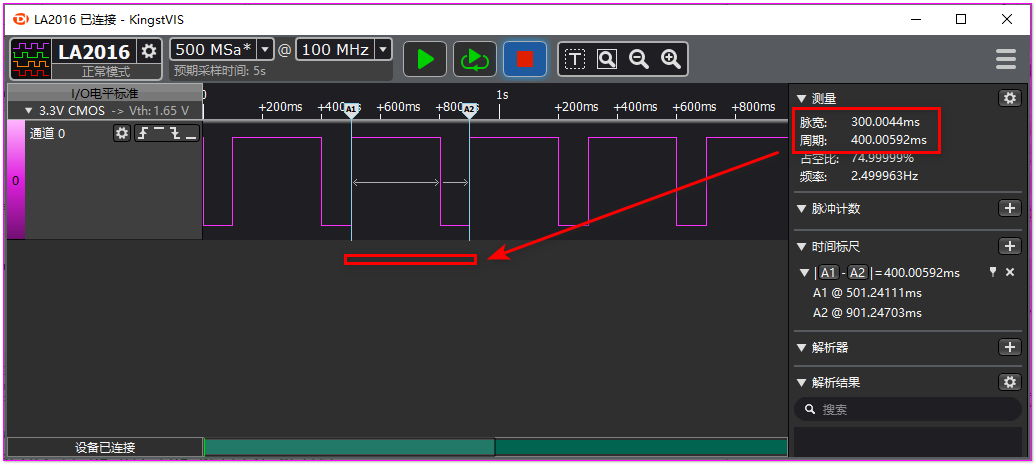

这里编写一个简单的LED闪烁示例,闪烁频率为 400ms,按照 300ms 亮-> 100ms 灭交替进行;

2.2.1 时钟

硬件的板子晶振为25MH,为了简单看看IP核使用,我们使用FPGA的PLL来生成一个20MHz的时钟:

- 点击 Tools -> MegaWizard Plug-In Manger 工具;

- 选择 IO/ -> ALTPLL,文件类型为 Verilog HDL;

- 输入时钟为25MHz;

- 不需要复位和lock信号;

- 时钟从25MHz到20MHz,因此需要设置为 MUL:4 , DIV:5,这样先倍频再降频到需要的值;

- 生成PLL核Verilog文件后,打开文件并根据PLL端口在工程中例化一个:

1 | wire sysclk; |

2.2.2 计数器

为了能达到400ms进行亮灭变化,需要计数器计数,时钟为20MHz,即周期为 50ns,这样只需要计数8000_000个即可达到LED闪烁需要的周期,然后分别在计数值为0和6000_000时候分别亮和灭即可;实现示例如下:

1 | always @(posedge sysclk or negedge rstn) |

3 编译

点击 start Analysis & Synthesis 进行分析综合电路,可以先使用这个选项分析代码是否正确;

点击 start compilation 进行综合、布局布线、FPGA编程文件等整个过程;

4 仿真

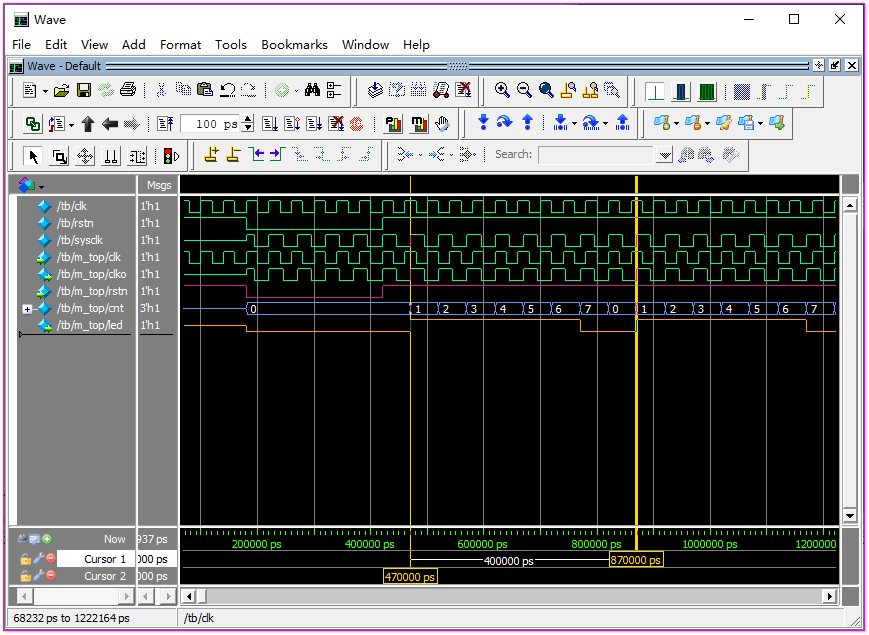

设计好模块后,一般先进行一次仿真,看是否符合预期;

为了减小仿真时间,先把计数减小,仿真正确后再改回以在硬件上测试;

- 编写Testbench

编写如下测试激励:

1 |

|

主要生成一个25MHz的时钟和一个复位信号;

- 仿真

点击项目设置,在EDA Tools设置中的simulation中选择 compile test bench,然后把编写的testbench文件添加进来,testbench name 要注意一样:

然后点击tools -> run simulation tool -> RTL simulation,打开仿真查看波形:

注:

(1)仿真时候,如果testbench产生的时钟和PLL输入时钟不相等时候,会出现PLL输出时钟不正确;

(2)PLL输出时钟需要等待一定的时间才能输出;

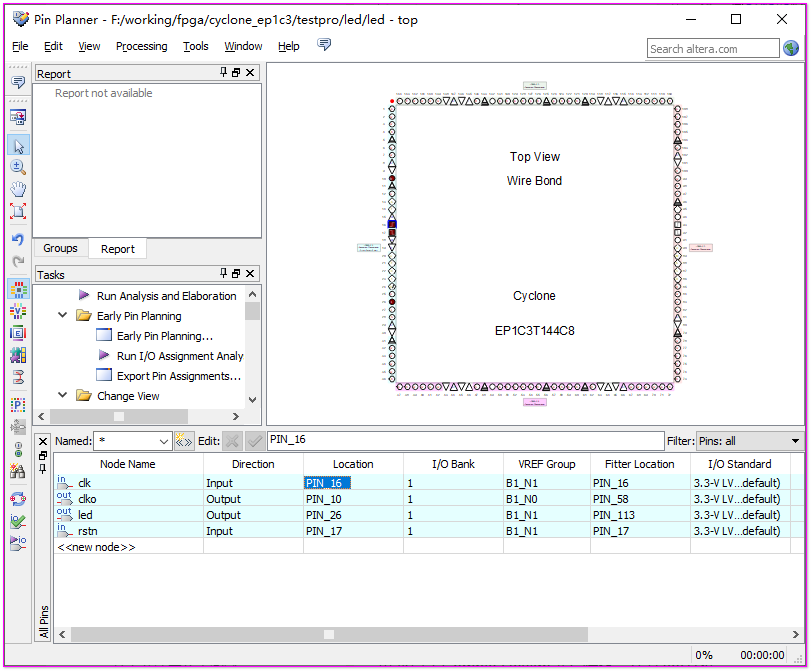

5 分配引脚

- 点击Pin Planner工具,进行引脚分配

在location位置,选择每个端口对应硬件的引脚进行分配;

6 硬件烧写测试

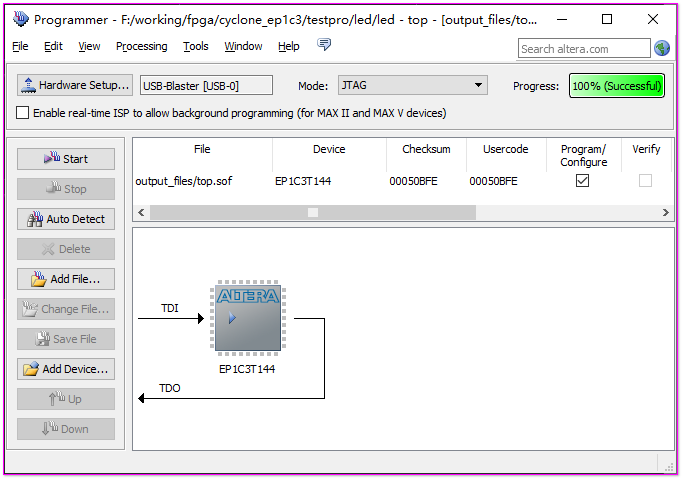

6.1 使用USB Blaster烧录

- 点击Programmer,打开烧写工具

- 在Hardware Setup中选择硬件连接的USB设备;

- Mode选择烧写模式:

- Active Serial Programming 为烧写到EPCS芯片掉电不会丢失,需要烧写的文件为pof;

- JTAG模式为烧写到FPGA,掉电会丢失,下载文件为sof;

6.2 实际测试

测试波形时间,可以看到与预期一致: