rt-thread入门1 Windows系统下在STM32上运行rt-thread OS

1 开发环境软件包:https://www.rt-thread.org/page/download.html 开发工具:keil5

2 开始步骤2.1 解压软件包下载的3.1.x版本,然后解压

2.2 打开工程在目录 rt-thread-3.1.4\bsp\stm32\stm32f103-mini-system 下直接打开keil5工程:project.uvprojx

2.3 适配自己的硬件我这里使用STM32F103C8T6小篮板,LED位于PC13引脚,因此不需要修改。 main 文件代码如下:

1234567891011121314151617181920212223242526272829303132333435/* * Copyright (c) 2006-2018, RT-Thread Development Team * * SPDX-License-Identifier: Apache-2.0 * * Change Logs: * Date Author Notes * 2019-03-08 obito0 first vers ...

RIOT-OS入门 Windows系统下在STM32上运行RIOT OS

1、开发环境1.1 软件和文档

RIOT OS:https://github.com/RIOT-OS/RIOT

windows上开发环境配置教程:https://github.com/RIOT-OS/RIOT/wiki/Build-RIOT-on-Windows-OS

1.2 主要步骤

下载编译工具 GNU Arm Embedded Toolchain gcc,然后将其放置到环境变量;

下载MinGW,并选择安装mingw32-base, mingw32-gcc-g++, msys-base和msys-mintty

安装完成后,将安装目录下 xx\msys\1.0\bin下的mintty建立桌面快捷方式,并设置目标为: xx\msys\1.0\bin\mintty.exe /bin/bash -l

打开桌面的mintty并执行mingw-get update更新

然后执行mingw-get install安装msys-wget, msys-zlib, msys-unzip, msys-mktemp

最后将mingw和msys下的bin目录添加到环境变量

...

vivado导出仿真波形文件

在vivado仿真中,没有提供直接导出波形文件的功能,我们要导出波形文件可以按照下面方式进行:

1、运行仿真后,在simulation界面的TCL中运行一下命令:

open_vcd

log_vcd [get_object /testbench/module/*] //这里选组要导出的信号,*表示模块module下的所有信号

run 50us //运行仿真

close_vcd

2、上述步骤完成后,我们就可以查看文件了,路径如下:项目工程\mcu.sim\sim_1\synth\timing\xsim\dump.vcd可以使用gtkwave直接打开查看信号如下:

GoLand常用快捷键

查询快捷键

CTRL+N 查找类

CTRL+SHIFT+N 查找文件

CTRL+SHIFT+ALT+N 查找类中的方法或变量

CTRL+B 快速打开光标处的类或方法

CTRL+ALT+B 找所有的子类

CTRL+SHIFT+B 找变量的类

CTRL+G 定位行

CTRL+F 在当前窗口查找文本

CTRL+SHIFT+F 在指定窗口查找文本

CTRL+R 在 当前窗口替换文本

CTRL+SHIFT+R 在指定窗口替换文本

ALT+SHIFT+C 查找修改的文件

CTRL+E 最近打开的文件

F3 向下查找关键字出现位置

SHIFT+F3 向上一个关键字出现位置

F4 查找变量来源

CTRL+ALT+F7 选中的字符查找工程出现的地方

CTRL+SHIFT+O 弹出显示查找内容

ALT+F1 查找文件所在目录位置

CTRL+H 显示类结构图

CTRL+Q 显示注释文档

CTRL+SHIFT+I 简短查看源定义

CTRL+SHIFT+P 查看表达式类型(在表达式上或者表达式末尾使用)自动代码

Alt+Enter 导入包,自动修正

CTRL+ALT+L 格式化代码

CTRL+ALT+I 自动缩 ...

STM32 CubeMX HAL库MH-Z19B获取CO2二氧化碳数据

1、说明(1)MCU为STM32F103C8,二氧化碳传感器使用型号MH-Z19B; (2)硬件连接:MH-Z19B的串口与STM32的串口2相连接; (3)MH-Z19B的HD引脚连接到STM32的一个引脚,可用于手动校准零点; (4)程序中使用HAL库,代码有CubeMX生成;

2、程序驱动头文件:mh_co2.h123456789101112131415#ifndef __MHCO2_H_#define __MHCO2_H_#include "stdbool.h"#include "string.h"#include "main.h"#include "usart.h"#include "gpio.h"void co2_init();void co2_sample(uint16_t *co2);#endif

驱动主文件:mh_co2.c123456789101112131415161718192021222324252627282930313233343536373839404 ...

STM32 CubeMX HAL库M24C02 EEPROM操作

1、说明(1)MCU为STM32F103C8,EEPROM型号M24C02; (2)硬件连接:EEPROM连接STM32的IIC1; (3)EEPROM的E0,E1,E2,WC脚连接地,因此其设备地址为:(0x50<<1),即0xA0; (4)程序中使用HAL库,代码有CubeMX生成;

2、程序驱动头文件:m24_eeprom.h12345678910111213141516171819\#ifndef __M24_EEPROM_H_#define __M24_EEPROM_H_#include "stdbool.h"#include "string.h"#include "main.h"#include "tim.h"#include "usart.h"#include "gpio.h"HAL_StatusTypeDef EEPROM_ReadByte(uint16_t MemAddress,uint8_t *data);HAL_StatusTypeD ...

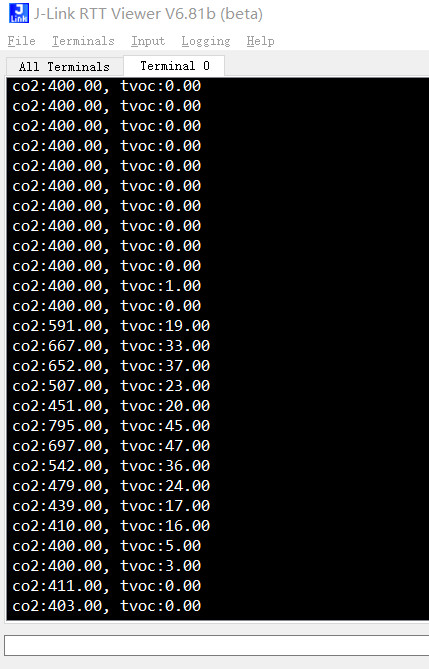

STM32 CubeMX HAL库使用SGP30获取CO2和VOC

1、说明(1)MCU为STM32F103C8,模块为SGP30; (2)硬件连接:SGP30连接STM32的IIC1; (3)SGP30的设备地址为:(0x58<<1); (4)程序中使用HAL库,代码有CubeMX生成;

2、程序驱动头文件:sgp30.h12345678910111213141516#ifndef __SGP30_H_#define __SGP30_H_#include "stdbool.h"#include "string.h"#include "main.h"#include "tim.h"#include "usart.h"#include "gpio.h"HAL_StatusTypeDef sgp30_init();HAL_StatusTypeDef sgp30_sample(float *co2, float *tvoc);#endif

驱动主文件:sgp30.c123456789101112131415161718192 ...

STM32 CubeMX HAL库使用SHT30获取温湿度

1、说明(1)MCU为STM32F103C8,温湿度芯片为SHT30; (2)硬件连接:SHT30连接STM32的IIC1; (3)SHT30的ADDR脚连接地,因此其设备地址为:(0x44<<1),即0x88; (4)程序中使用HAL库,代码有CubeMX生成;

2、程序驱动头文件:sht30.h12345678910111213#ifndef __SHT30_H_#define __SHT30_H_#include "stdbool.h"#define SHT_ADDR (0x44<<1)uint8_t sht30_init();uint8_t sht30_sample(float *t, float *h);#endif

驱动主文件:sht30.c1234567891011121314151617181920212223242526272829303132333435363738394041424344454647484950515253545556575859606162636465666768697071727374757677 ...

NFC模块PN532使用

1、PN532数据包格式:(1)正常数据包:

00

00 FF

LEN

LCS

TFI

PD0…PDn

DCS

00

00 :序列头

00 FF :起始号

LEN :数据包长度,包含TFI

LCS :数据长度校验和,LEN+LCS = 0

TFI :命令; D4表示主机到PN532,D5表示PN532到主机

PD0…PDn:数据

DCS :数据校验和,TFI+PD0+…+PDn = 0

00 :序列结尾

(2)应答包:

00

00 FF

00 FF

00

00 :序列头

00 FF :起始号

00 FF :应答包

00 :序列结尾

(3)非应答包:

00

00 FF

FF 00

00

00 :序列头

00 FF :起始号

FF 00 :没有应答

00 :序列结尾

(4)加长数据包:

00

00 FF

FF

FF

LENM

LENL

LCS

TFI

PD0…PDn

DCS

00

在正常情况下,只能发送256个字节的数据,PN532提供一种特殊的格式可以发送更 ...

FreeCAD基础操作

1、快捷方式1.1、3D导航

1.2、快捷键2、工作台2.1 PartDesign零件工作台

2.2 Kicad可以结合Kicad进行PCB边框设计。